Vias act as critical interconnects between the copper layers inside multilayer printed circuit boards (PCBs), enabling traces to smoothly transition between layers carrying signals across entire boards. However, blindly selecting via sizes risks signal quality issues or manufacturing defects.

Determining appropriate via dimensions requires balancing electrical performance, routing constraints, stackup constructions, drilling limitations and application environments. This article summarizes key considerations when choosing standard via sizes for robust PCB design along with visual sizing tables covering common drill requirements.

Importance of Optimal Via Sizing

Selecting inappropriate via sizes severely impacts PCB functionality:

Impedance Discontinuities – Excessive via dimensions reflect signals causing ringing

Crosstalk Problems – Larger anti-pads increase coupling to adjacent traces

Thermal Management – Tiny vias bottleneck heat transfer to inner planes

Signal Losses – Thin traces transitioning to thick barrels degrade performance

Manufacturing Defects – Undersized aspect ratios risk fabrication yields

Reliability Hazards – Cracking or delamination across barrel interfaces

Therefore balancing electrical, thermal mechanical needs proves vital when defining workable via sizes, spacing, pad styles and anti-pad dimensions.

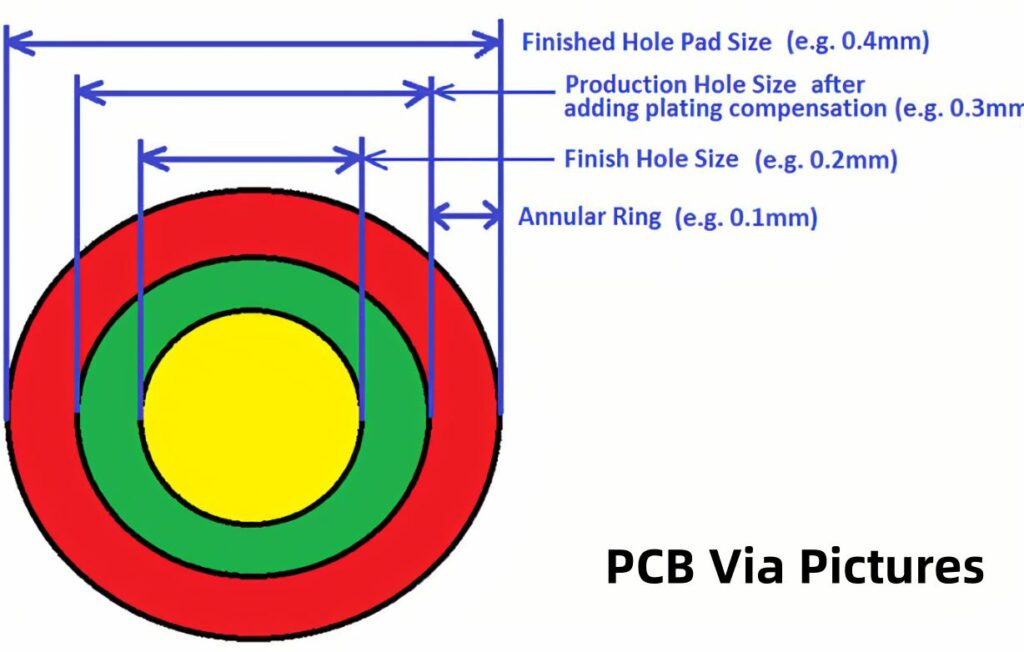

Typical PCB Via Geometries

Vias contain several characteristic dimensions vital for determining appropriate sizes:

Drill Hole – Circular interior width clearing copper

Barrel Depth – Vertical span between connecting layers

Annular Ring – Copper clearance around hole to pad edge

Anti-Pad – Expanded pad area devoid of copper

Land Pad – Base pad interfacing trace terminals

Finish – Plating across drilled holes

Fig. 1. – Via Geometries and PCB Stackup

Standard via sizing depends primarily on PCB thickness dictating drill aspect ratios.

Selecting Optimum Via Sizes

Ideal via dimensions vary across six key factors:

1. Drilling Capabilities

- Mechanical Drill Bit Sizes – Available standard bit diameters (0.25mm-3mm)

- Registration Accuracy – Hole centering repeatability

- Aspect Ratio Limits – Maximum drill depth:width ratios

- Stack Alignment – Accumulated through-hole positional errors

- Hole Wall Quality – Barrel roughness and resin smear

This defines minimum production drill sizes and feasible aspect ratios.

2. Current Levels

- PCB Copper Weights – Heavier 2oz+ copper sustain more current

- Barrel Plating – Thicker plated copper lowers resistance

- Thermal Loads – Wider paths needed handling higher powers

- Quantity – Parallel vias share total current

This provides cross-sectional area sizing to meet electrical load requirements.

3. Impedance Control Needs

- Signal Edge Rates – Faster rise times need wider barrels

- Dielectric Types – Materials impact impedance

- Stackup Construction – Plane spacing influences performance

- Propagation Delays – Excessive via spans slow transmission

- Nearby Ground Vias – Additional returns lower loop inductance

Impedance discontinuity minimization assists signal quality.

4. Routing Constraints

- Escape Routing – Fanout clearance around fine pitch devices

- Component Keepouts – Spacing from passive/connector footprints

- High Density Layouts – Compact spacing amid congestion

- Plane Splits – Span clearance between split reference layers

- Separation Rules – Distance between adjacent hole centers

This defines integration density amid other board features.

5. Thermal Management

- Connected Plane Layers – More layers dissipate heat faster

- Barrel Plating – Enhanced metallization lowers conduction loss

- Anti-Pad Dimensions – Thermal relief size impacts transfer

- High Power Areas – Dense thermal vias aid cooler operation

- Perimeter Placement – Distributes heating minimizing hotspots

Thermal via integration assists heat dissipation from hot devices.

6. Manufacturing Process Capabilities

- Registration Accuracy – Tighter precision permits smaller annular rings

- Plating Thickness – Thicker uniform finishes prevent barrel cracks

- Etching Capability – Fine line widths facilitate compact anti-pads

- Lamination Alignment – Layer misalignments impact hole positions

- Panel Stresses – Warping risks reliability across stressed boards

Real-world process variances limit via construction options.

Carefully reviewing these interdependent electrical, mechanical and thermal tradeoffs allows identifying application-specific via sizing sweet spots maximizing performance.

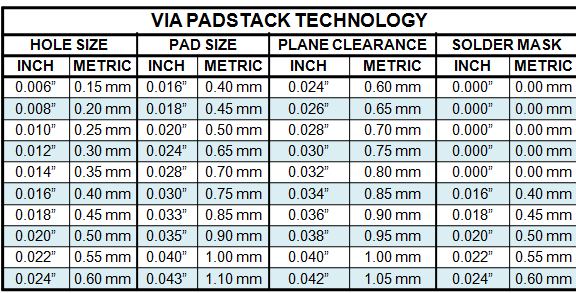

Typical Industry Standard Via Sizes

These Industry Council on Electronics Packaging (ICEP) via sizes see widespread use balancing functionality across typical boards:

1. High Density Interconnect (HDI) Vias

Microvias with diameters under 8mils (0.2mm) suit ultra-fine line HDI boards needing 3x routing density versus standard PCBs. HDI laser drilling enables high-volume stacked microvia fabrication.

Typical HDI Microvia Sizes

- Drill Size – 2 to 8mils

- Annular Rings – 4 to 6mils depending on registration accuracy

- Anti-Pads – Around 16 to 20mils

HDI microvias assist integrating ultra-compact functionality like wafer level packages (WLP).

2. Thin PCB Vias

These matchCapabilities of high precision mechanical drilling equipment used for cost-sensitive consumer electronics PCBs around 1.6mm thickness.

Common Thin PCB Via Specifications

- Drill Size – 8 to 12mils diameter vias

- Aspect Ratio – 5:1 to 10:1 drill depth to diameter ratio

- Annular Ring – Typically 6mils clearance

- Anti-Pads – Around 20mils depending on trace spacing

Machine accuracy rather than aspect ratios often size vias in thin PCBs.

3. Standard Thickness PCB Vias

SVia diameters for conventional PCBs span around 1.6mm to 2.5mm using widespread FR-4 glass epoxy substrates utilize these sizes:

Typical Medium PCB Via Dimensions

- Drill Size – 12 to 20mils diameter holes

- Aspect Ratio – 3:1 to 5:1 drill ratio for reliable copper plating

- Annular Ring – 8mils clearance accommodates registration variances

- Anti-Pads – Approximately 24mils fit common routing grids

Cost savings from standard drill sizes makes these dimensions popular for wide production runs.

4. Thick PCB Vias

PCBs exceeding 2.5mm demand larger vias sustaining aspect ratios without exponentially decreasing fabrication yields attaining sufficient plating quality for protecting inner barrel surfaces against cracks or dendritic growth.

Large Via Sizes for Thick PCBs

- Drill Size – 20 to 28mils or even larger holes on high layer counts

- Aspect Ratios – Keep between 3:1 to 5:1 for most materials

- Annular Ring – At least 8 to 10mils; increase further allowing registration slop

- Anti-Pads – 30mils+ helps accommodate annular ring growth

Here electrical needs determine diameters rather than drill costs.

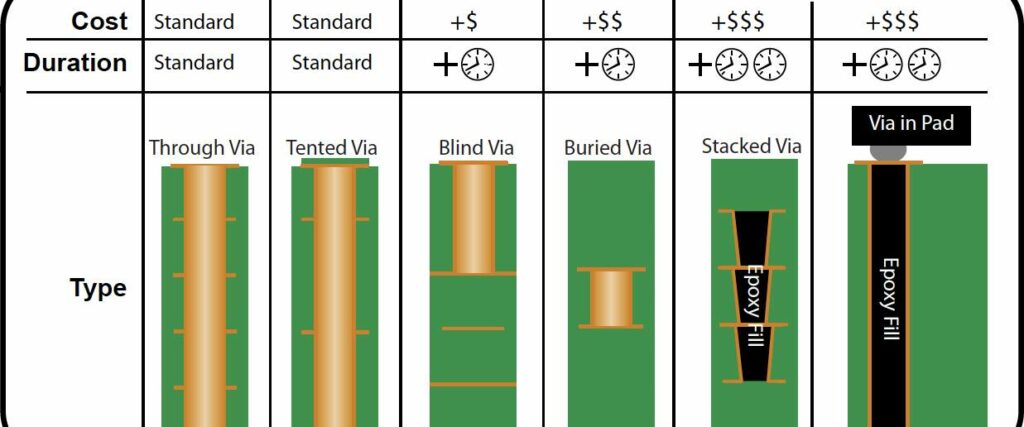

Recommended Via Styles

Various via configurations suit different applications:

Through Holes – Span entire board sandwiching layers

**Blind Vias ** – Only link outer and adjacent inner layers

Buried Vias – Nestled entirely between inner layers

Stacked Vias – Sequentially connected hole chains

Skipped Vias – Isolated barrels bypassing plane layers

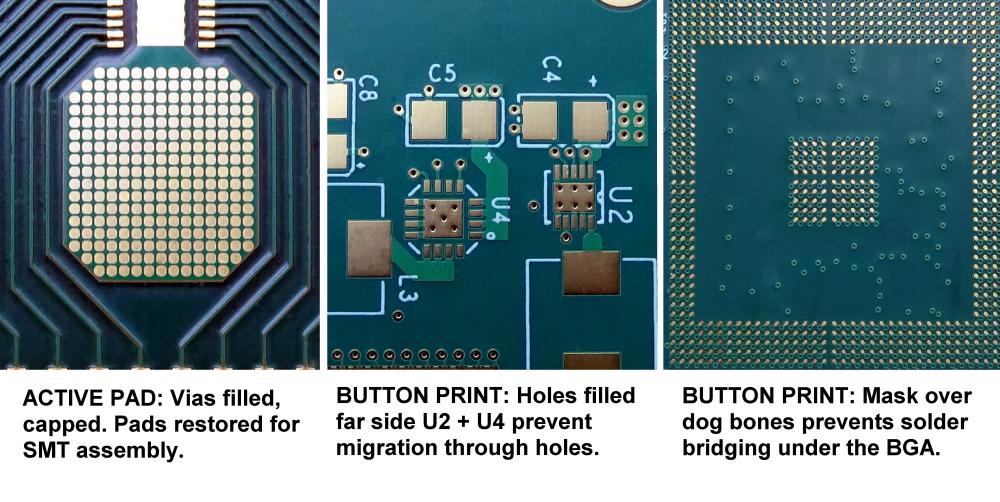

Filled Vias – Enhanced metallization or insulation fills holes

Thermal Reliefs – Anti-pads prevent plane soldering

Each style impacts signal performance, routing capacities, layer transitions and heat flows based on connection schemes optimizing electrical or thermal needs.

Guidelines for Determining Optimum Via Sizes

Use these best practice sizing tips:

- Start drill selection based on manufacturer’s mechanical capabilities and process maturity

- Define annular ring widths factoring in hole position registration accuracy

- Keep anti-pad dimensions the bare necessity clearing annular rings

- Lower drill depths for tighter aspect ratio control; use laser drilling for deeper microvias

- Leverage IPC-2226/ICEP-50 standards catching industry best practices

- Account for inner layer misalignments accommodating reasonable fabrication tolerances

- Utilize thicker 2oz-3oz copper, enhanced ENIG/Immersion Silver plating sustaining high reliability

- Validate designs with impedance simulations assessing performance impacts before release

Following such practical step-by-step evaluation allows systematically navigating the myriad interdependent co-optimization decisions necessary for striking optimal application-specific via sizing delivering the essential interconnectivity and current-carrying capacities sustaining functionality across fielded PCB solutions.

Impact of Inappropriate Via Sizes

Selecting incorrect via sizes hampers board performance:

Undersized Vias – Thin barrels fail carrying specified current levels risking blown traces

Oversized Vias – Large anti-pads increase coupling noise corrupting signals

Excessive Aspect Ratios – Deep holes with inaccurate barrels lower fabrication yields

Inadequate Hole Wall Plating – Skews impedance while allowing micro-cracks degrading signal quality over time

Insufficient Annular Rings – Reduces structural integrity risking plated through hole failures

Incorrect Anti-Pad Dimensions – Causes solder flooding or insufficient thermomechanical anchoring

Therefore comprehensive evaluations determining sweet spot dimensions satisfying electrical, thermal, structural, and functional thresholds prove mandatory before finalizing interface via stacking.

Using Oval Shaped Vias

Oval vias elongated along routing paths conserve spacing between adjacent rows when fanning out fine pitch ICs compared to circular pads occupying larger footprints for equivalent via barrel areas:

Fig. 2 – Reduced pitch oval vias versus square anti-pads for equivalent via area

However, oval vias also demonstrate detriments:

- Requires specialized mechanical drill heads increasing production costs

- Oblong anti-pads increase coupling versus compact circular contours

- Estimating current capacity and impedance requires analysis of narrowest cross-section diameter

- Reduces via redundancy with only one drill diameter path limiting current sharing compared to dual parallel circular vias

Therefore selective employment only where escape routing limitations dictate enable maximizing advantage without impacting overall stackup construction flexibility or performance.

Future PCB Via Trends

Various technologies seek improving via integration densities, electrical performance and manufacturing yields:

Laser Drilled Vias – Tapered hole profiles using355nm Nd:YAG lasers allow high-density stacked microvias

Copper Filled Vias – Enhanced metallization improves electrical/thermal conductivity

Embedded Component Vias – Integrates tiny surface mount resistors/capacitors inside boards

Buried Capacitance Vias – Ultra-thin dielectric layers between adjacent hole barrels create capacitive connections

Plated Through Hole Reinforcement – Additional pad anchors using copper pillars or solder anchoring increase via pull strength

Reliability Enhancement Coatings – Conformal films using paralynes, Parylenes or Teflon aid surface passivation withstanding temperature humidity biases prolonging product lifetimes across challenging deployment regimes.

Automated Inspection Systems – Detect subtle plating voids or resin smear along hole walls signalling latent defects through precise laser microtomography without necessitating regular hole cross-sectioning further improving yields.

Thereby incremental material and manufacturing process improvements sustain continual enhancements gradually pushing size limits enabling next-generation PCBs scalability trajectories meeting unrelenting consumer electronics miniaturization demands.

Key Points Summary

The essential guidelines for identifying optimum PCB via sizes include:

- Drilling Tool Bit Availability – Standard tool catalog hole sizes often determine lower bounds

- Electrical Needs – Current levels and signal quality dictate conductor cross-sections

- Thermal Management – Heat load dispersal requires sufficiently thick via barrels

- Stackup Arrangements – Signal reference planes spacing impacts impedance

- Mechanical Needs – Withstand vibration/shock considering thermal expansion effects

- Fabrication Process Maturity – Custom sizes may yield unproven results lacking repeatability

- Testing with Prototypes – Correlate impedance/thermal simulations with measurements

- Adherence to IPC Standards – Leverage industry guidelines capturing best practices

By prudently weighing these multiple interdependent selection factors, designers settle on judicious PCB via sizes delivering the essential signal/power integrity, noise immunity and current capacities sustaining flawless performance across application operating conditions.

Conclusion

This guide examined the various electrical, mechanical, thermal and functional tradeoffs involved in picking appropriate via sizes, styles and dimensions capable of meeting necessary current carrying capacities, impedances, signal quality needs, integration densities, reliability thresholds and manufacturing process limitations. Rather than blindly laying out PCB holes basis availability, comprehensive co-optimization balancing conduction requirements, fabrication yields, registration accuracy and performance budgets allows harnessing maximum value from PCB interfaces across deployed lifecycles using standard via dimensions already proven from years of empirical scrutiny.

Frequently Asked Questions

How do you determine via placement on a PCB?

Optimum via positioning minimizes signal path lengths by logically locating holes at appropriate junctions across traces routings between various surface mount components pinouts to necessary internal PCB layers transitioning signals based shortest connections preserving signal integrity necessary for higher speed links while taking care to meet drilling centroids registration demand for assembly houses when fanning out finer pitched devices.

Do vias act as antennas on PCBs?

Yes, by virtue of forming unavoidable gaps across reference planes otherwise providing shielding, vias allow electromagnetic egress coupling noise emissions from fast switching circuits to radiate externally functioning as compromised antennas connected directly into transmission paths unless adequate guard banding using multiple ground vias surround each individual hole confining stray radiation leakage meeting electromagnetic compatibility directives.

Why are thermal reliefs used around vias connected to planes?

Excessive heat conducted from high power traces connected through vias start saturating entire ground or power planes raising overall PCB temperatures leading to operational drifts or even laminate delamination damage. Hence appropriate anti-pad dimensions forming thermal breaks avoid solder fillet connections across plane layers facilitating heat localization while still retaining necessary structural and electrical bonding across interfacing trace pads.

How are microvias used in HDI PCBs?

Laser drilled microvias spanning well under 0.15mm facilitate 3x higher interconnect densities stacking connections between layers otherwise unachievable using standard drills. HDI constructions allow embedding completely encapsulated passive components inside the PCB using microvias enabling even denser integration for next generation electronics.

What are back-drilled PCB vias?

Achieving multi-Gbps signaling rates across PCB backplanes demands minimizing via stub lengths at line card mating connectors otherwise introducing impedance discontinuities degrading eye diagrams below receiver thresholds. This needs selectively back-drilling barrel portions reference plane connections after primary PCB fabrication retaining only pad extensions forming soldered joints thereby removing problematic stubs though at increased production expenses.